Nice machine studying (ML) analysis requires nice programs. With the rising sophistication of the algorithms and {hardware} in use at the moment and with the size at which they run, the complexity of the software program needed to hold out day-to-day duties solely will increase. On this put up, we offer an summary of the quite a few advances made throughout Google this previous 12 months in programs for ML that allow us to assist the serving and coaching of complicated fashions whereas easing the complexity of implementation for finish customers. This weblog put up additionally highlights our analysis on leveraging ML itself to assist enhance and design the following generations of system stacks.

Distributed programs for ML

This 12 months, we have made vital strides in bettering our programs to higher assist large-scale computation in ML and scientific computing generally. The Google TPU {hardware} has been designed with scaling in thoughts since its inception, and every year we try to push the boundaries even additional. This 12 months, we designed state-of-the-art serving methods for giant fashions, improved automated partitioning of tensor applications and reworked the APIs of our libraries to verify all of these developments are accessible to a large viewers of customers.

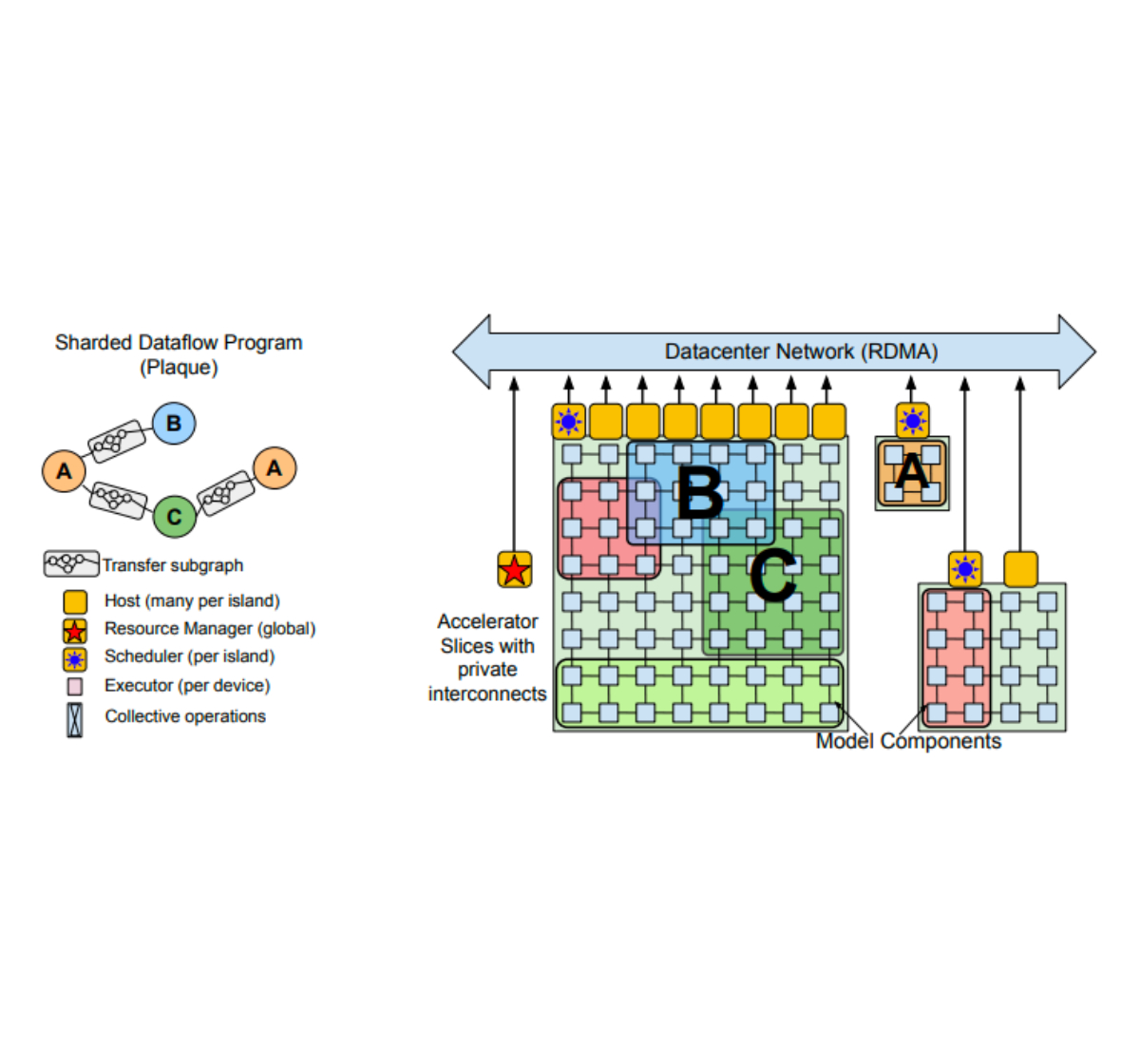

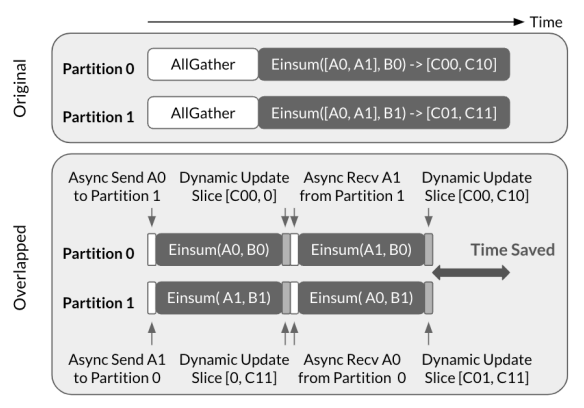

One in every of our greatest effectivity enhancements this 12 months is the CollectiveEinsum technique for evaluating the massive scale matrix multiplication operations which are on the coronary heart of neural networks. Not like beforehand fashionable SPMD partitioning methods that separate communication from device-local computation, this method makes use of the quick TPU ICI hyperlinks to overlap them, resulting in as much as 1.38x efficiency enhancements. This algorithm was additionally a key part of our work on effectively scaling Transformer inference, which presents all kinds of methods that commerce off between latency and {hardware} utilization, reaching state-of-the-art mannequin FLOPs utilization (MFU) of 76% in throughput-optimized configurations.

|

| An illustration of AllGather-Einsum with 2-way intra-layer mannequin parallelism, proposed in CollectiveEinsum technique. Prime: Illustration of non-overlapped execution. Backside: Illustration of the CollectiveEinsum approach. |

Now we have additionally built-in SPMD-style partitioning as a firstclass idea into each TensorFlow, with the DTensor extension, and JAX, with the redesigned array kind. In each libraries, tensors that appear full to the programmer will be transparently sharded over a variety of gadgets simply by attaching declarative structure annotations. In actual fact, each approaches are appropriate with current code written for single-device computations that may now scale right into a multi-device program, normally with none code modifications!

Integrating SPMD partitioning into the core of our ML frameworks signifies that with the ability to infer and optimize the way in which array applications are mapped onto a bigger set of gadgets is essential for efficiency. Prior to now, this motivated the event of GSPMD, an necessary milestone on this space. Nevertheless, GSPMD depends closely on heuristics, and it nonetheless typically requires non-trivial choices to be made manually, which frequently leads to suboptimal efficiency. To make partitioning inference totally automated, we collaborated with exterior colleagues to develop Alpa, a totally automated system that explores methods for each operator-level (mannequin) parallelism and pipeline parallelism between bigger sub-computations. It efficiently matches hand-tuned efficiency on fashionable fashions similar to Transformers, however can be able to efficiently scaling up different fashions, similar to convolutional networks and mixture-of-experts fashions that usually trigger current automated strategies to wrestle.

|

| Alpa overview. The inter-operator identifies one of the best ways to assign a subgraph to a submesh. The intra-operator move finds one of the best intra-operator parallelism plan for every pipeline stage. Lastly, the runtime orchestration generates a static plan that orders the computation and communication. |

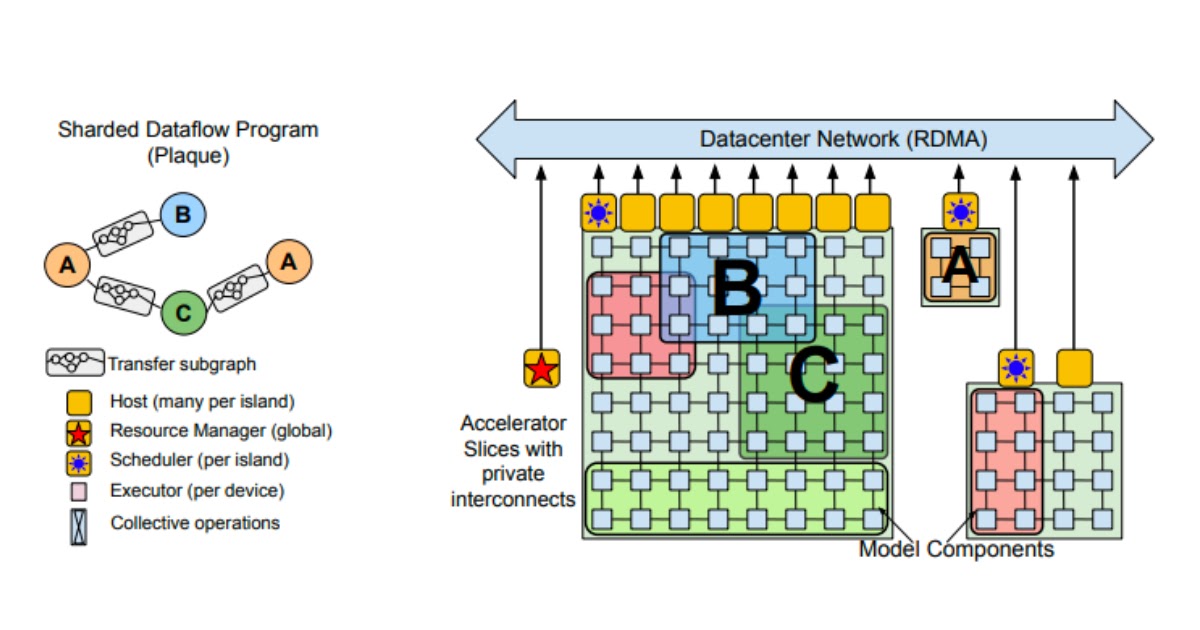

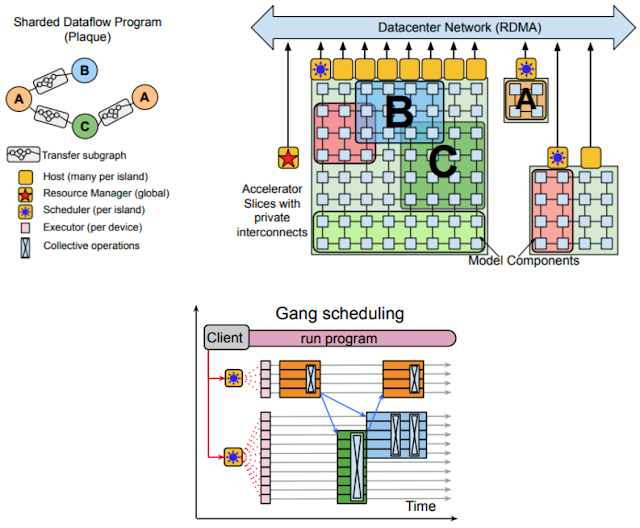

In an identical vein, the lately revealed Pathways system provides a further layer of virtualization on high of the same old TPU runtime — accelerators are managed by long-lived processes as an alternative of being allotted on to customers. A single finish person can then connect with an arbitrary variety of Pathways-controlled gadgets and write their program as if all of the gadgets have been hooked up on to their course of, although in actuality they could even span a number of information facilities. Because of Pathways: (1) job startup time will be lowered, (2) it’s simpler to realize fault tolerance, and (3) multitenancy turns into a viable choice, enabling a number of jobs to be executed concurrently for much more environment friendly {hardware} utilization. The benefit with which Pathways permits computation spanning a number of TPU pods is essential, because it lets us keep away from future scaling bottlenecks.

|

| Pathways overview. Prime Left: Distributed computation expressed as a Directed Acyclic Graph. Prime Proper: The useful resource supervisor allocates digital slices of accelerator meshes for every compiled operate (e.g., A, B, and C). Backside: Centralized schedulers for gang-schedule computations which are then dispatched by per-shard executors. (See paper for particulars.) |

One other notable launch is TensorStore, a brand new library for multi-dimensional array storage. TensorStore is especially helpful for coaching giant language fashions (LLMs) with multi-controller runtimes, the place each course of solely manages a subset of all parameters, all of which have to be collated right into a constant checkpoint. TensorStore offers database-grade ensures (ACID) for environment friendly and concurrent multi-dimensional array serialization into many storage backends (e.g., Google Cloud Storage, numerous filesystems, HTTP servers) and has been efficiently used for compute-intensive workloads similar to PaLM and reconstructions of the human cortex and fruit fly mind.

Programming languages for ML

The robustness and correctness of our technical infrastructure are important for ML efforts, which is why we stay dedicated to making sure that it’s constructed on a sound technical and theoretical foundation, backed by cutting-edge analysis in programming languages and compiler development.

We continued investing within the open-source MLIR compiler infrastructure, constructing a extra controllable, composable and modular compiler stack. As well as, a lot progress has been made in code technology for sparse linear algebra and it’s now potential to generate each dense and sparse code from nearly an identical MLIR applications. Lastly, we additionally continued the event of the IREE compiler, getting ready it to be used on each highly effective computer systems positioned in information facilities and cellular gadgets similar to smartphones.

On the extra theoretical aspect we explored methods to formalize and confirm the code-generation methods we use. We additionally revealed a novel method used to implement and formalize automated differentiation (AD) programs, that are central to ML libraries. We decomposed the reverse-mode AD algorithm into three impartial program transformations, that are considerably less complicated and simpler to confirm, highlighting the distinctive options of JAX’s implementation.

Leveraging programming language methods, similar to summary interpretation and program synthesis, we efficiently lowered the variety of assets required to carry out a neural structure search (NAS). This effort, 𝛼NAS, led to the invention of extra environment friendly fashions with out degradation in accuracy.

Prior to now 12 months, we revealed a variety of new open-source libraries within the JAX ecosystem, Rax and T5X being simply two examples. With the continued effort round jax2tf, JAX fashions can now be deployed on cellular gadgets utilizing TensorFlow Lite and on the net utilizing TensorFlow.js.

{Hardware} accelerators & ML

{Hardware} design for ML

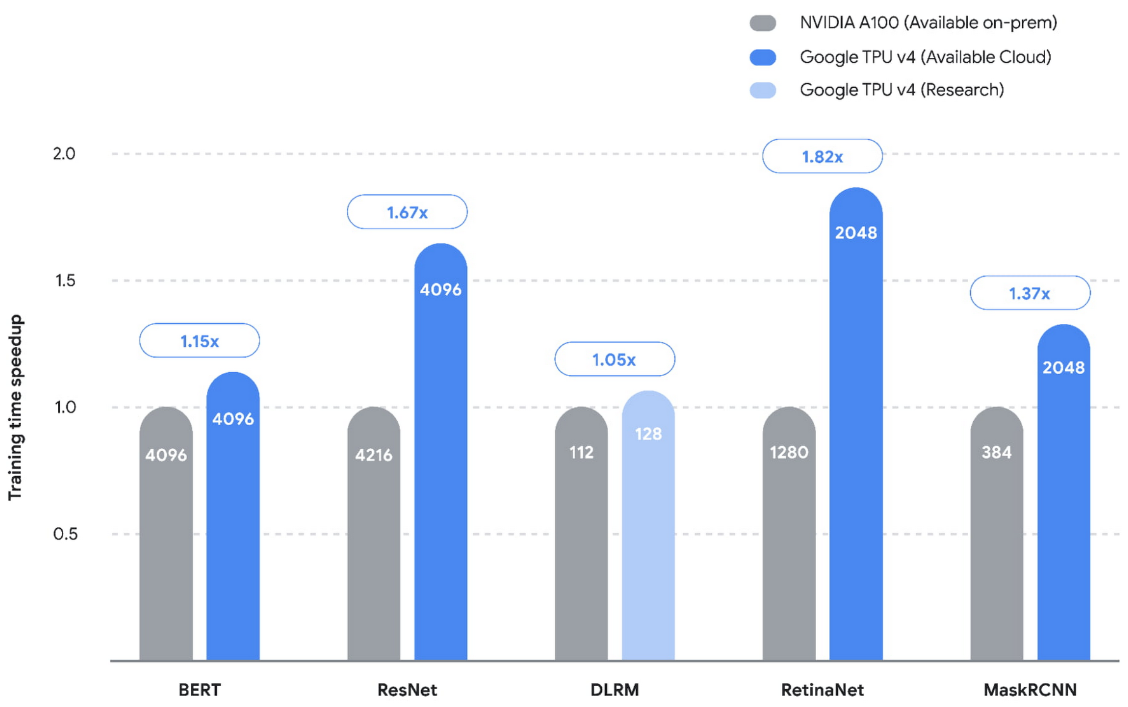

Using custom-made {hardware}, similar to TPUs and GPUs, has proven large advantages by way of each efficiency achieve and vitality effectivity (therefore lowering the carbon footprint). In a current MLPerf competitors, we set new efficiency data on 5 benchmarks on TPUs v4, attaining speedups which are on common 1.42x larger than the following quickest submission. Nevertheless, with a view to sustain with current advances, we’re additionally growing custom-made {hardware} architectures for particular fashionable fashions.

|

| TPUs demonstrated vital speedup in all 5 revealed benchmarks (MLPerf 2.0) over the quickest non-Google submission (NVIDIA on-premises). Taller bars are higher. The numbers contained in the bars symbolize the amount of chips / accelerators used for every of the submissions. |

Nevertheless, constructing a brand new {hardware} accelerator incurs excessive preliminary price and requires vital growth and deployment time. To make single-workload accelerators viable, the design cycle time must be lowered. Full-stack Search Approach (FAST) addresses this downside by introducing a {hardware} accelerator search framework that concurrently optimizes information path, scheduling, and necessary compiler choices. FAST introduces an approximate template able to describing various forms of architectures and versatile reminiscence hierarchy leading to accelerators that enhance single-workload efficiency per Thermal Design Energy (recognized to extremely correlate with efficiency per Complete Price of Possession) by 3.7x in comparison with TPU v3. This exhibits that single-workload accelerators might be sensible for moderate-sized datacenter deployments.

ML for {hardware} design

To automate the chip design course of as a lot as potential, we proceed to push the capabilities of ML at numerous phases of the {hardware} design, together with high-level architectural exploration, verification, and placement and routing.

We lately open-sourced a distributed RL infrastructure referred to as Circuit Coaching, together with a circuit surroundings described in our current Nature paper. We used this infrastructure in manufacturing to supply macro placements for the newest technology of TPU chips. Tackling architectural exploration, PRIME introduces an ML-based method for looking out {hardware} design house that makes use of solely current information (e.g., from conventional accelerator design efforts) with none additional {hardware} simulation. This method alleviates the necessity to run time-consuming simulations, even when the set of goal purposes modifications. PRIME improves efficiency over state-of-the-art simulation-driven strategies by about 1.2x–1.5x whereas lowering the simulation time by 93%–99%. AutoApprox robotically generates approximate low-power deep studying accelerators with none accuracy loss by mapping every neural community layer to an applicable approximation stage.

|

| PRIME makes use of logged accelerator information, consisting of each possible and infeasible accelerators, to coach a conservative mannequin, which is used to design accelerators whereas assembly design constraints. PRIME designs accelerators with as much as 1.5x smaller latency, whereas lowering the required {hardware} simulation time by as much as 99%. |

{Hardware}-dependent mannequin design

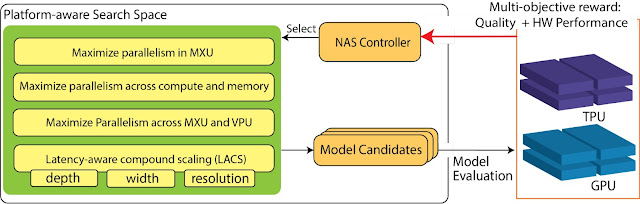

Whereas NAS has proven large functionality in discovering state-of-the-art fashions by way of accuracy and effectivity, it’s nonetheless restricted by lack of {hardware} data. Platform-aware NAS addresses this hole by incorporating data of the {hardware} structure into the design of the NAS search house. The ensuing EfficientNet-X mannequin is 1.5x–2x sooner than EfficientNet on TPU v3 and GPU v100, respectively, with comparable accuracy. Each platform-aware NAS and EfficientNet-X have been deployed in manufacturing, demonstrating vital accuracy positive factors and as much as ~40% effectivity enchancment for numerous manufacturing imaginative and prescient fashions. NaaS goes even additional by trying to find neural community architectures and {hardware} architectures collectively. Utilizing this method on Edge TPUs, NaaS discovers imaginative and prescient fashions which are 2x extra vitality environment friendly with the identical accuracy.

|

| Overview of platform-aware NAS on TPUs/GPUs, highlighting the search house and search goals. |

ML for navigating constrained search areas

Other than altering the {hardware} and the workload for higher effectivity, we will additionally optimize the center layer, together with the partitioner, which maps the workload onto a number of gadgets, and the compiler, which interprets the workload right into a low-level presentation understood by the {hardware}. In earlier years, we demonstrated how we will apply ML to seek out higher system placement and compiler choices. Prior to now 12 months, we additional explored this path and located that many optimization search areas are closely constrained, the place legitimate options are fairly sparse.

To handle this problem, we developed a number of methods to allow a realized mannequin to successfully navigate a constrained search house. Telamalloc employs a mixture of ML mannequin plus heuristics to decide when a number of choices can be found, and leverages a constraint solver to deduce additional dependent choices. Telamalloc accelerates the reminiscence allocation move within the Edge TPU compiler in comparison with a manufacturing Integer Linear Programming method and permits necessary real-world fashions that might not in any other case be supported.

“A Transferable Strategy for Partitioning Machine Studying Fashions on Multi-Chip-Modules” proposes a barely completely different method. It applies reinforcement studying (RL) to suggest the choices in a single step, and asks the constraint solver to regulate the proposed resolution to be legitimate. For a BERT mannequin on an Edge TPU-based multi-chip mesh, this method discovers a greater distribution of the mannequin throughout gadgets utilizing a a lot smaller time funds in comparison with non-learned search methods.

ML for large-scale manufacturing programs

We additionally deployed ML to enhance effectivity of assorted large-scale programs working in manufacturing. We lately launched MLGO, the primary industrial-grade common framework for integrating ML methods systematically within the LLVM infrastructure. MLGO can exchange heuristics in LLVM with an RL coverage to make optimization choices. When testing on a set of inside large-scale purposes, we discovered that the educated coverage can scale back binary measurement by 3%–7% when optimizing inlining choices and may enhance throughput by 0.3% ~1.5% when optimizing register allocation choices. Inside our manufacturing ML compiler, XLA, a realized price mannequin revealed a couple of years again, was lately deployed to information the number of optimum tile sizes of TPU kernels for high ML workloads, saving ~2% of the whole TPU compute time in our information facilities general.We additionally lately changed an current heuristic in YouTube cache alternative algorithm with a brand new hybrid algorithm that mixes a easy heuristic with a realized mannequin, bettering byte miss ratio on the peak by ~9%.

|

| Illustration of MLGO throughout inlining. “#bbs”, “#customers”, and “callsite peak” are instance caller-callee pair options. |

AI & sustainability

Given the worldwide local weather change disaster, there was comprehensible concern in regards to the environmental influence of ML. In a current paper, we confirmed that by following finest practices, ML practitioners can scale back carbon dioxide equal emissions (CO2e) from coaching by orders of magnitude. We name the practices the “4Ms”

- Mannequin. Step one is to pick essentially the most environment friendly ML mannequin structure. For instance, Primer runs ~4x sooner on the identical {hardware} whereas attaining the identical high quality scores than the favored Transformer developed 4 years earlier.

- Machine. The second observe is to make use of essentially the most vitality environment friendly pc obtainable. For instance, when the Transformer mannequin was first revealed in 2017, a well-liked GPU was the Nvidia P100. Utilizing a current processor optimized for ML coaching, similar to TPU v4, improves efficiency per Watt by ~15x.

- Mechanization. Computer systems for coaching wanted to be housed in an information heart. Massive cloud information facilities are usually ~1.4x extra energy-efficient than the everyday smaller on-premise information heart.

- Map. The largest shock in our investigation was the influence on the cleanliness of the vitality provide by choosing one of the best location. Furthermore, within the cloud, location is the simplest of the 4 elements to alter. The distinction between a typical location and a effectively chosen location will be ~9x, even throughout the identical nation.

On this instance, multiplying the 4Ms collectively yields a 4x × 15x × 1.4x × 9x or ~750x discount in CO2e over 4 years by following one of the best practices over the coaching of the unique Transformer mannequin utilizing GPUs of 2017.

We’re persevering with to discover this house and in 2023 we will likely be releasing an additional research that demonstrates how one can scale back the CO2e of present mannequin coaching by as much as 20x by fastidiously deciding on the machine, mechanization and site of coaching.

Concluding ideas

As the sphere of ML advances, we proceed our funding in growing high-performance, energy-efficient, and easy-to-use programs and infrastructure to allow fast exploration of latest concepts. On the identical time, we proceed to discover the aptitude of ML to enhance the efficiency of complicated programs and automate labor-intensive duties in system design.

Google Analysis, 2022 & past

This was the second weblog put up within the “Google Analysis, 2022 & Past” sequence. Different posts on this sequence are listed within the desk under:

| * Articles will likely be linked as they’re launched. |